|

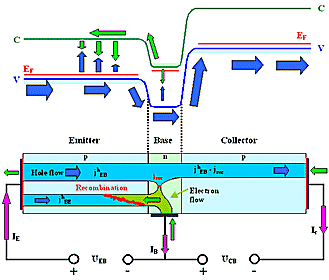

Essentials of the bipolar transistor: |

|

|

|

|

High emitter doping (NDon for npn transistor

here) in comparison to base doping NAc for large current amplification factor g

= IC/IB. | |

|

|

NDon/NAc »

k = injection ratio. | |

| | |

| |

| |

| g | » |

NDon

NAc | · |

æ

ç

è | 1 – |

dbase

L | ö

÷

ø

|

|

| |

|

| |

|

|

|

Small base width dbase (relative to diffusion length L)

for large current amplification. | |

|

|

Not as easy to make as the band-diagram suggests! |

|

|

| |

| |

|

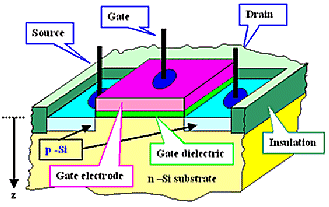

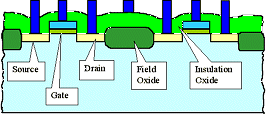

Essentials of the MOS transistor: |

|

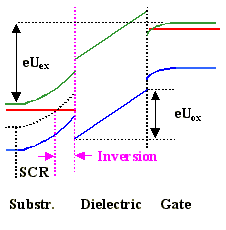

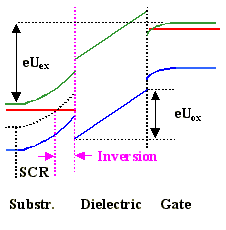

| | Band diagram for inversion |

|

|

|

Gate voltage enables Source-Drain current |

|

|

|

Essential process. Inversion of majority carrier type in channel below gate by:

- Drive intrinsic majority carriers into bulk by gate voltage with same sign as majority carriers.

- Reduced majority concentration nmaj below gate increases minority carrier concentration nmin

via mass action law

| |

| | |

| |

| |

| |

|

|

|

- An inversion channel with nmin > nmaj develops below the gate as soon

as threshold voltage UTh is reached.

- Current now can flow because the reversely biased pn-junction between either source or drain and the region below

the gate has disappeared.

| |

| | |

| |

|

|

The decisive material is the gate dielectric (usually SiO2).

Basic requirement is: | | |

|

|

High capacity CG of the gate electrode - gate dielectric -

Si capacitor = high charge QG on electrodes = strong band bending = low threshold voltages

UG | |

|

|

|

It follows:

- Gate dielectric thickness dDi

Þ High breakdown field strength UBd

- Large dielectric constant er

- No interface states.

- Good adhesion, easy to make / deposit, easy to structure, small leakage currents, ...

|

|

Example:

U = 5 V, dDi = 5 nm Þ E = U/dDi

= 107 V/cm !!

er(SiO2) = 3.9 |

|

|

Integration means: | |

|

|

|

1. Produce a large number (up to 1.000.000.000) of transistors

(bipolar or MOS) and other electronic elements on a cm2 of Si |

|

|

|

2. Keep thoses elements electrically insulated from each other. |

|

|

|

3. Connect those elements in a meaningful way to produce a system / product. |

|

| |

| |

| |

|

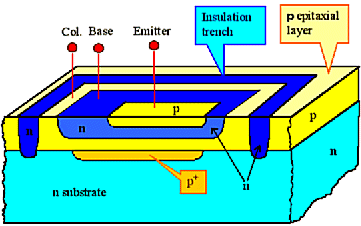

An integrated bipolar transistor does not resemble the textbook picture at all,

but looks far more complicated Þ. |

|

|

|

|

This is due to the insulation requirements, the process requirements, and the need to interconnect

as efficiently as possible. | |

|

|

The epitaxial layer cuts down on the number of critical diffusions, makes insulation easier,

and allows a "buried contact" structure. | |

| | |

| |

|

|

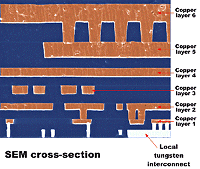

Connecting transistor / elements is complicated; it has to be done on several

levels | |

|

|

|

Materials used are Al ("old"), Cu ("new"), W, (highly

doped) poly-Si as well as various silicides. | |

|

|

Essential properties are the conductivity s of the conductor,

the dielectric constant er of the intermetal dielectric, and the resulting

time constant t = s · er

that defines the maximum signal transmision frequency through the conducting line. |

|

| |

| |

| |

|

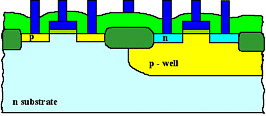

Integrating MOS transistors requires special measures for insulation (e.g.

a field oxide) and for gate oxide production | |

|

|

|

Since a MOS transistor contains intrinsically a capacitor (the gate "stack"),

the technology can be used to produce capacitors, too. | |

| | |

| |

|

|

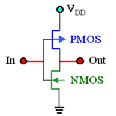

CMOS allows to reduce power consumption dramatically. |

|

|

|

|

The process, however, is more complex: Wells with different doping type need to be made. |

|

| |

| |

| |

|

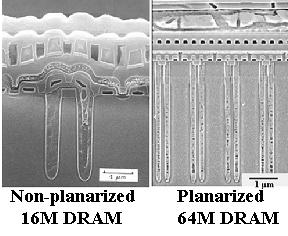

Using the third dimension (depth / height) might become necessary for integrating

"large" structures into a small projected are (example: trench capacitor in DRAMs Þ). |

|

|

|

|

Unwanted "topology", however, makes integration more difficult. |

|

|

|

Planarized technologies are a must since about 1995! Þ |

|

| |

| |

| |

|

It ain't neither easy nor cheap! |

|

| Property | Number |

| Feature size | 0,2 µm |

| No. metallization levels | 4 - 7 |

| No. components | > 6 · 108 (Memory) |

| Complexity | > 500 Process steps |

| Cost (development and 1 factory) |

ca. $ 6 · 109 |

|

|

Typical wafer size for new factories (2007) : 300 mm diameter, 775

µm thickness, flatness in lower µm region | |

|

|

|

Chip size a few cm2, much smaller if possible |

|

|

|

Yield Y = most important parameter in chip production = % of chips on a wafer

that function (= can be sold). | |

|

|

Y = 29 % is a good value for starting production |

|

|

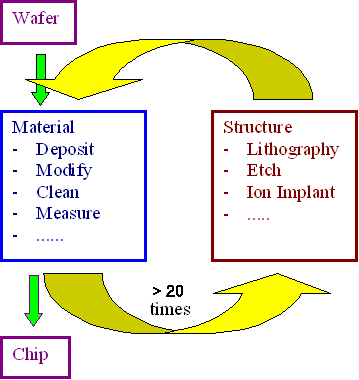

Chip making = running about 20 times (roughly!!) through "materials"

- "structuring" loop. | |

|

|

About 400 - 600 individual processing steps (= in / out of special "machine")

before chip is finished on wafer | |

|

|

More than 30 processing steps for packaging (after separation of chips by cutting) |

|

|

|

Simple estimate: 99.9% perfection for each processing step meansY < 70

%. | |

|

Dirt in any form - as "particles" on the surface of wafer, or as "contamination"

inside the wafer is almost always deadly | |

|

|

|

Particles with sized not much smaller than minimum feature sizes (i.e. < 10

nm in 2007) will invariably cover structures and lead to local dysfunction of a transistor or whatever. |

|

|

|

Point defects like metal atoms in the Si lattice may precipitate and cause local short

circuits etc. from the "inside", killing transistors |

|

|

|

One dysfunctional transistor out of 1.000.000.000 or so is enough to kill a chip! |

|

|

| |

| |

|

Being extremely clean is absolutely mandatory for high Yields Y! |

| |

|

|

Use cleanrooms and hyper-clean materials! |

| |

|

|

It won't be cheap! | |

|

© H. Föll (Electronic Materials - Script)