Available online at www.sciencedirect.com

Microelectronic Engineering 84 (2007) 313-318

www.elsevier.com/locate/mee

# Si/Al<sub>2</sub>O<sub>3</sub>/ZnO:Al capacitor arrays formed in electrochemically etched porous Si by atomic layer deposition

Marianna Kemell<sup>a,\*</sup>, Mikko Ritala<sup>a</sup>, Markku Leskelä<sup>a</sup>, Emmanuel Ossei-Wusu<sup>b</sup>, Jürgen Carstensen<sup>b</sup>, Helmut Föll<sup>b</sup>

<sup>a</sup> Laboratory of Inorganic Chemistry, Department of Chemistry, University of Helsinki, P.O. Box 55, FI-00014 Helsinki, Finland <sup>b</sup> Faculty of Engineering, University of Kiel, Kaiserstrasse 2, D-24143 Kiel, Germany

> Received 24 July 2006; received in revised form 13 October 2006; accepted 21 October 2006 Available online 16 November 2006

### Abstract

High surface area Si/Al<sub>2</sub>O<sub>3</sub>/ZnO:Al capacitors were formed in electrochemically etched porous silicon. The Al<sub>2</sub>O<sub>3</sub> dielectric and the ZnO:Al top electrode were deposited by atomic layer deposition in high aspect ratio porous Si. A single capacitor with a typical area of about 1 mm<sup>2</sup> consisted of about 10<sup>5</sup> pores. Effective capacitance densities were between 2.0 and 2.5  $\mu$ F/cm<sup>2</sup>, i.e., approximately 30 times higher than for a planar capacitor prepared under identical conditions, illustrating the effect of the enhanced surface area in the porous structure. © 2006 Elsevier B.V. All rights reserved.

Keywords: Macroporous silicon; Electrochemical etching; Atomic layer deposition; Thin films; High aspect ratio capacitor

# 1. Introduction

The number of passive components (inductors, resistors and capacitors) on a circuit board exceeds the number of integrated circuits in almost any application [1]. Because passive components occupy a large share of the space on a circuit board, miniaturization has been looked for. This is especially important in wireless products with increasing performance and functionality, where the share of passive components is highest. On the other hand, the minimum allowable size of a passive component is determined by the ability to handle and assemble the components on the board [2]. Traditionally, passive components have been discrete, i.e., single inductors, resistors and capacitors in their individual packages attached on the board with individual solder joints [1]. Research on integrating multiple passive components in a single package has been going on for some time, and various approaches have been studied [1,3]. One approach is to use thin-film deposition methods for the formation of several passive

\* Corresponding author. *E-mail address:* marianna.kemell@helsinki.fi (M. Kemell). components on a single substrate (for example Si) [2,3]. These arrays or networks of passive components can then be packaged in single IC-like packages and attached on the circuit board [2]. In addition to saving space on the board, integrated passive components add to the reliability of the product since fewer solder joints are required [1].

High value capacitor arrays with capacitances from tens of nanofarads to several microfarads are needed as decoupling and energy storage capacitors [4]. In order to minimize the footprint area occupied by the capacitor array on the circuit board/package, capacitor designs with increased capacitance densities are required.

As seen from the well-known equation for a parallel plate capacitor (Eq. (1)), the capacitance density increases with decreasing insulator thickness, increasing insulator permittivity, and increasing effective surface area of the capacitor without increasing its footprint area

$$C = \varepsilon \varepsilon_0 A / t, \tag{1}$$

where C is the capacitance,  $\varepsilon$  is the relative permittivity of the insulator material,  $\varepsilon_0$  is the permittivity of vacuum  $(8.85 \times 10^{-12} \text{ F/m})$ , A is the area of the capacitor, t is the thickness of the insulator. Commonly used insulator

<sup>0167-9317/\$ -</sup> see front matter @ 2006 Elsevier B.V. All rights reserved. doi:10.1016/j.mee.2006.10.085

materials in thin film capacitors include  $SiO_2$ ,  $Si_3N_4$ ,  $Al_2O_3$  and  $Ta_2O_5$  [5–13].

When aiming to extremely high capacitance densities, it is necessary to combine the benefits achieved with a high permittivity insulator material and an increased effective surface area. With Si as the substrate material, the effective surface area can be increased by, for example, electrochemical etching that is a well-known method for the preparation of high aspect ratio structures in Si [14]. For example, electrochemical etching of moderately doped n-type Si under backside illumination in properly chosen conditions results in the formation of deep, straight, cylindrical macropores [14]. Electrochemically formed macroporous Si has in fact been used successfully for the preparation of high aspect ratio capacitors with layered SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> insulators [11,12].

The increased surface area requires the ability to deposit thin films with conformal coverage and uniform film thickness on the walls of a high aspect ratio structure. For most thin film deposition methods this is extremely challenging, if not impossible.

Atomic layer deposition (ALD) is a chemical gas phase thin film deposition method that can be used for the deposition of metal oxides, nitrides and metals [15-17]. Because of its self-limiting growth mechanism, ALD is well suited for coating high aspect ratio structures such as deep pores and trenches. Film growth by ALD occurs via alternating saturative surface reactions. The precursor vapors are pulsed into the reactor one at a time, and the precursor pulses are separated by inert gas purges. After each precursor pulse and the subsequent purge, the substrate surface is saturated by a (sub)monolayer of that precursor. Since the gas phase is free of the first precursor, the next precursor reacts only with the adsorbed surface layer. Thus the film growth occurs (sub)monolayer by (sub)monolayer, and film thicknesses can be accurately controlled by the number of the deposition cycles. Films deposited by ALD exhibit excellent conformality and compositional uniformity over large and complex-shaped substrates.

Preliminary results on high aspect ratio capacitors with ALD-grown layered  $Al_2O_3/Ta_2O_5/Al_2O_3$  and  $Al_2O_3/HfO_2$ / $Al_2O_3$  insulators were reported recently [13]. The porous Si substrates in that study were formed by dry etching.

This paper describes a simple, non-lithographic process for the preparation of high density  $Si/Al_2O_3/ZnO:Al$ capacitor arrays by combining electrochemically formed high aspect ratio macroporous Si with atomic layer deposition of the insulator and the top electrode.  $Al_2O_3$  was chosen as the insulator because of its relatively high permittivity and ZnO:Al as the top electrode material because of its easy etching.

#### 2. Preparation of the n-Si/Al<sub>2</sub>O<sub>3</sub>/ZnO:Al capacitors

### 2.1. Preparation and properties of the porous Si

The macroporous Si was prepared by electrochemical etching. Pieces of n-type (100) Si with a resistivity of

$1-4 \Omega$  cm were used. In order to remove the native SiO<sub>2</sub> layer, the Si pieces were first dipped in 10 wt% aqueous HF solution for approximately 1 min. The electrical contact was subsequently formed by scratching the back surface of the Si piece, and rubbing some liquid In–Ga solder on the scratch.

The etching was done in a thermostated cell at 20 °C. Aqueous 4 wt% HF solution with a few drops of detergent was used as the electrolyte. Backside illumination was done using a LED array. The etch potential was 1.5 V, and the etch current density was decreased in a preprogrammed manner from the initial value of 8 mA/cm<sup>2</sup> to the final value of  $7 \text{ mA/cm}^2$  during the etching. The etch current was controlled by adjusting the intensity of the illumination, i.e., the voltage used for driving the LED array [14,18]. The pores were formed by random nucleation, i.e., no initial pits were formed. The resulting pore diameters were approximately 2 µm, with similar pore wall thicknesses. Thus, about half of the surface was covered with pores. According to a simple calculation, the density of pores on the surface was about  $1.6 \times 10^7$ /cm<sup>2</sup>. The etch duration was usually 100 min which resulted in a porous layer with a depth of 50 µm. Thus the aspect ratio of the structure was about 25 and the enhancement of the surface area caused by the porous structure was about 50-fold.

### 2.2. Thin film deposition

Prior to the ALD growth, the porous Si substrate was dipped in aqueous 10 wt% HF solution in order to remove the native SiO<sub>2</sub> layer. The Si substrate was then rinsed with water and blown dry with  $N_2$ .

The capacitors were prepared by depositing approximately 50 nm of Al<sub>2</sub>O<sub>3</sub> and 180 nm ZnO:Al by atomic layer deposition (ALD). The depositions were done at 250 °C in a flow-type F-120 ALD reactor (ASM Microchemistry Ltd, Finland) [19] that was operated under a pressure of about 10 mbar using N<sub>2</sub> as the carrier and purging gas. Trimethylaluminum (TMA), dimethylzinc (DMZ), and H<sub>2</sub>O were used as the Al, Zn, and O precursors, respectively. The precursors were evaporated in their external reservoirs and led to the reactor through needle and solenoid valves. TMA and H<sub>2</sub>O sources were kept at room temperature and DMZ at -20 °C. In order to ensure adequate diffusion of the precursor vapors and the gaseous byproducts in and out of the deep pores, prolonged pulse and purge times were used. The pulse times for TMA and H<sub>2</sub>O were doubled and purge times tripled as compared to those normally used for flat substrates in this reactor. For DMZ, only the purge time was increased.

The Al<sub>2</sub>O<sub>3</sub> film was deposited using precursor pulse lengths of 2 s and purge lengths of 3 s for both TMA and H<sub>2</sub>O. The growth cycle was repeated 500 times. ALD of Al<sub>2</sub>O<sub>3</sub> from TMA and H<sub>2</sub>O is a well-known process and the excellent conformality of Al<sub>2</sub>O<sub>3</sub> grown from Al(CH<sub>3</sub>)<sub>3</sub> and H<sub>2</sub>O has been demonstrated earlier [20,21]. The ZnO:Al films were deposited according to [22]. The DMZ pulse and purge lengths were 0.2 s and 2 s, respectively, and the H<sub>2</sub>O pulse and purge lengths were 2 s and 3 s, respectively. 3% of the ZnO pulses were replaced by a sequence containing a 7 s purge, a 2 s TMA pulse, and a 10 s purge. The total pulsing sequence of 30 ZnO pulses + 1 TMA pulse was repeated 33 times. The resistivities of the ZnO:Al films were  $5-10 \times 10^{-3} \Omega$  cm, in agreement with those reported in the literature [22].

The film thicknesses were estimated afterwards from FESEM micrographs and were found to be in agreement with the deposition rates obtained on planar substrates.

# 2.3. Contact formation, device area definition and electrical measurements

The back contacts were made by evaporating an Al film (thickness about 75 nm) on the back side of the Si substrate, and by contacting a thin Cu wire to the Al film using In as a solder.

The front contacts were prepared by electron beam evaporation of Al dots (thickness about 75 nm) with 1 mm diameters on the ZnO:Al film. The device areas were defined by carefully etching the ZnO:Al film from the area between the dots with 2.5 M HCl. Using the above-mentioned etch technique, it is difficult to define the device area precisely, and thus the area may vary from device to device. Therefore the area of each dot was measured and estimated separately afterwards. The device areas were between about 0.7 and 1.33 mm<sup>2</sup>. The capacitance–voltage curves were recorded with a HP4284A precision LCR meter using the parallel circuit mode. The ac voltage applied to the

capacitor was 50 mV and the frequency of the ac signal was 10 kHz.

## 3. Results and discussion

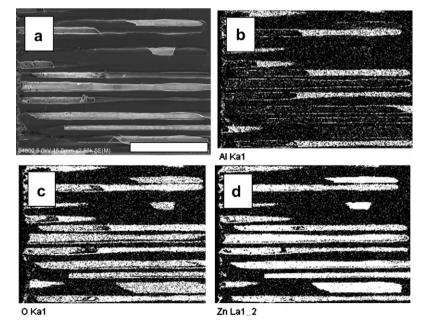

Fig. 1 shows a cross-section view of the high aspect ratio capacitor structure and the corresponding elemental maps for Al, Zn and O. The elemental maps show that EDS signals from Al, Zn and O are detected from the entire depth (50  $\mu$ m) of the porous Si layer. The inhomogeneity of the signals is due to partial peeling off of the films due to cross-section sample preparation by fracturing.

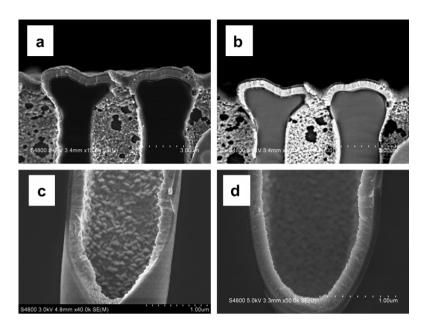

The secondary electron and backscattered electron images in Fig. 2 show details of the capacitor structure where all the layers are seen. The conformal growth of the amorphous Al<sub>2</sub>O<sub>3</sub> and the polycrystalline ZnO:Al films along the pore walls from the top all the way to the bottom is clearly seen. The film thicknesses along the pores were found to be uniform. Thus it can be concluded that the pulse and purge times applied here were sufficiently long to produce uniform films conformally on the pore walls. Fig. 2 shows, however, "pits" in the ZnO film (maybe also in  $Al_2O_3$ ) near the top of the porous layer. These pits were observed only near the top of the porous layer and are therefore suspected to result from the wet etching process that was used for the device area definition. With a better device area definition method this problem can naturally be avoided.

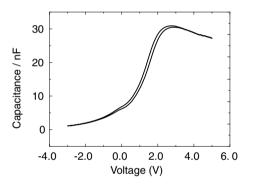

The effective capacitance densities measured from the high aspect ratio capacitors were between 2.0 and 2.5  $\mu$ F/cm<sup>2</sup> (normalized to the footprint area). Fig. 3 shows an example of a capacitance–voltage plot of a high aspect

Fig. 1. (a) A cross-section FESEM image and corresponding elemental maps for, (b) Al, (c) O and (d) Zn. The elemental maps were acquired with an Oxford INCA Energy 350 energy dispersive X-ray spectrometer (EDS) connected with a Hitachi S-4800 field emission scanning electron microscope (FESEM). Scale bar =  $20 \ \mu m$ .

Fig. 2. Details from the top (a,b), middle (c) and from the bottom (d) imaged with secondary (a, c, d) and backscattered electrons (b). The images were acquired with a Hitachi S-4800 field emission scanning electron microscope (FESEM).

Fig. 3. Capacitance–voltage plot for a high aspect ratio  $Si/Al_2O_3/ZnO:Al$  capacitor. Device footprint area was 1.33 mm<sup>2</sup>.

ratio capacitor. The device with the highest capacitance density  $(2.5 \,\mu\text{F/cm}^2)$ , or  $25 \,\text{fF/}\mu\text{m}^2$ ) had a footprint area of  $1.33 \,\text{mm}^2$  which corresponds to about  $2.1 \times 10^5$  pores.

Both Lehmann et al. [11] and Roozeboom et al. [12] have reported ultra high aspect ratio MOS capacitors formed in electrochemically prepared macroporous Si. In both studies, the pore diameters were similar to those in this work, about  $2 \,\mu m$ , but the pores were deeper, 150– 165 µm, resulting in about a 100-fold surface area enhancement [11,12]. The insulator consisted of a layered  $SiO_2/$  $Si_3N_4/SiO_2$  (ONO) structure with a total thickness of about 30 nm [11,12]. The capacitors of Roozeboom et al. [12] showed effective capacitance densities of  $10 \,\mu\text{F/cm}^2$ , i.e., about four times higher than those reported in this paper. Taking into account the different insulator thicknesses and permittivities, the lower capacitance densities observed in this work can be partly, but not completely, explained by the differences in the surface area enhancement factors. Based on the 50-fold surface area enhancement caused by the porous structure in this work, a 50-fold capacitance

enhancement was expected as compared to planar capacitors prepared under identical conditions. The observed capacitance enhancement was only approximately 30-fold, however. This may indicate a parasitic capacitance in series with the device. The origin of this parasitic capacitance is most likely related to the Si substrate and/or to the ZnO:Al conductor. This idea is supported by the fact that the conductivity of the porous Si sidewalls in MOS capacitors is usually increased by phosphorus doping prior to the insulator formation [11–13]. Furthermore, phosphorus-doped polysilicon is commonly used as the top electrode [11-13]. Therefore, it seems likely that the lower than expected capacitances in this study are related to the unoptimal properties of the Si substrate. A third possible reason for the lower than expected performance is SiO<sub>2</sub> formation between the Si substrate and the Al<sub>2</sub>O<sub>3</sub> film. On the other hand, a recent study [23] indicates that no interfacial SiO<sub>2</sub> formation should occur during the ALD growth of Al<sub>2</sub>O<sub>3</sub> from TMA and H<sub>2</sub>O.

Klootwijk et al. [13] reported capacitance densities of about 100 nF/mm<sup>2</sup> (10  $\mu$ F/cm<sup>2</sup>) for their high aspect ratio MOS capacitors. The porous Si substrate was prepared by dry etching. The porous layer was about 35 µm deep and had pore diameters of 1.5-2 µm and pore intervals of about 3 µm. The porous structure was reported to cause a 20-fold increase of the surface area. The insulators were three-layer structures of either Al<sub>2</sub>O<sub>3</sub>/Ta<sub>2</sub>O<sub>5</sub>/Al<sub>2</sub>O<sub>3</sub> or  $Al_2O_3/HfO_2/Al_2O_3$ . This approach was considered to be beneficial in aiming to high capacitance densities together with minimal leakage currents. All insulator films were deposited by ALD and had thicknesses of 6-12 nm for  $Ta_2O_5$ , 5–10 nm for HfO<sub>2</sub> and 2–3 nm for Al<sub>2</sub>O<sub>3</sub> [13]. Analogously to the results in the current study, the observed capacitance densities were 20-50% lower than expected. On the basis of TEM analysis, Klootwijk et al. [13] listed

several reasons for the unexpectedly low capacitance densities: roughness of the porous Si surface, variations in the thickness and crystallinity of the insulator films along the pore depth, and the presence of native  $SiO_2$  [13].

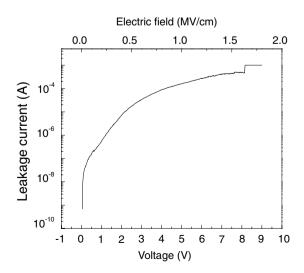

In this work, the lowest leakage current at 5 V (which corresponds to an electric field of 1 MV/cm) was  $1.6 \times 10^{-4}$  A for a device with a footprint area of 1.13 mm<sup>2</sup>. Thus the effective leakage current density is  $1.4 \times 10^{-2}$  A/cm<sup>2</sup> (normalized to the footprint area). Taking into account the 50-fold enhancement of the surface area caused by the porous structure, the "real area" leakage current density was  $1.6 \times 10^{-4}$  A /(50 × 1.13 mm<sup>2</sup>) =  $2.8 \times 10^{-4}$  A/cm<sup>2</sup>. On the other hand, as seen from Fig. 4, the leakage current was considerably lower at 2.5 V where the capacitance was at maximum. The leakage current at 2.5 V was only  $1.7 \times 10^{-5}$  A which corresponds to an effective leakage current density of  $1.5 \times 10^{-3}$  A/ cm<sup>2</sup> and "real area" current density of  $3.0 \times 10^{-5}$  A/cm<sup>2</sup>. Still, the leakage currents were considerably higher than those reported in the literature for ALD-grown Al<sub>2</sub>O<sub>3</sub> on hydrogen-terminated Si [23]. For comparison, Klootwijk et al. [13] measured leakage currents of about  $10^{-3}$  A/cm<sup>2</sup> at 1 V (presumably normalized to the footprint area) for their high aspect ratio capacitors with  $Al_2O_3/Ta_2O_5/$ Al<sub>2</sub>O<sub>3</sub> insulator layers. Taking into account the 20-fold surface area enhancement by the porous structure, a simple calculation results in a "real area" current density of about  $5 \times 10^{-5}$  A/cm<sup>2</sup>. The high aspect ratio Si/SiO<sub>2</sub>/TaN capacitors of Black et al. [9] showed also similar effective leakage current densities as the capacitors in this work, about  $10^{-3}$  A/cm<sup>2</sup> at 1 V. On the other hand, the leakage currents reported by Lehmann et al. [11] for their high aspect ratio capacitors with layered SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> insulators were several orders of magnitude lower than those measured in this work.

Fig. 4. Leakage current in accumulation as a function of applied voltage for a high aspect ratio Si/Al<sub>2</sub>O<sub>3</sub>/ZnO:Al capacitor. Device footprint area was 1.13 mm<sup>2</sup>.

The high leakage currents observed in this work may be somehow related to the ZnO:Al conductor. It is possible that the wet etching process may have damaged also the  $Al_2O_3$  layer. The pits in the ZnO:Al layer are clearly visible in the FESEM micrographs (see Fig. 2) but it is difficult to say if the damage goes all the way to the  $Al_2O_3$  layer or not. The idea of ZnO:Al-related problem is further supported by the fact that also the planar devices prepared in this work under identical conditions showed high leakage currents. On the other hand it must be noted that the leakage current requirements for decoupling capacitors are not as strict as for some other applications [4,24]; according to [24], the leakage current of a decoupling capacitor is acceptable if its magnitude is considerably below the total current required by the IC.

Combination of ALD with electrochemically prepared macroporous Si offers several advantages for the preparation of capacitor arrays: a wide selection of materials can be deposited conformally with very accurate composition and thickness control. Moreover, capacitor arrays with different values can be achieved relatively easily by combining porous and flat areas, and by patterning the top electrodes with features of varying sizes.

### 4. Conclusions

A simple, non-lithographic process was developed for the preparation of high value capacitor arrays in electrochemically formed macroporous Si. High aspect ratio Si/Al<sub>2</sub>O<sub>3</sub>/ZnO:Al capacitors were prepared by atomic layer deposition of the insulator and the top electrode in the macroporous Si. The high surface area as compared to the footprint area resulted in capacitance densities between about 20 and 25 fF/ $\mu$ m<sup>2</sup>. Leakage currents were high, however, which may result from unoptimal wet etching process used for the device area definition. Better results are to be expected by optimizing the device area definition process, thus resulting in lower leakage currents. The wide selection of insulator and conductor materials available by ALD allows the preparation of a variety of capacitor arrays with different values.

# Acknowledgements

The authors thank the Academy of Finland (Project Nos. 201564, 209739) for financial support.

### References

- R.K. Ulrich, W. Schaper, in: Integrated Passive Components Technology, IEEE, 2003 (Chapter 1).

- [2] R. Ulrich, U. Schaper, IEEE Spectrum (July) (2003) 26-30.

- [3] B. Arbuckle, E. Logan, D. Pedder, Solid State Technol. 43 (2000) 84– 86, 88,90.

- [4] R. Ulrich, Circuit World 30 (2003) 20-24.

- [5] P. Gill, M. Miller, B.Y. Nguyen, Microelectron. Eng. 56 (2001) 169– 175.

- [6] C. Linder, A. Huegli, H. Friedli, Solid State Technol. 46 (2003) 52– 53, 56.

- [7] A. Farcy, J. Torres, V. Arnal, M. Fayolle, H. Feldis, F. Jourdan, M. Assous, J.L. Di Maria, V. Vidal, Microelectron. Eng. 70 (2003) 368–372.

- [8] C. Thomason, L. Schaper, J. Morgan, S. Burkett, R. Ulrich, in: Proceedings of the 55th Electronic Components and Technology Conference, 2005, IEEE, pp. 779–782.

- [9] C.T. Black, K.W. Guarini, Y. Zhang, H. Kim, J. Benedict, E. Sikorski, I.V. Babich, K.R. Milkove, IEEE Electron. Device Lett. 25 (2004) 622–624.

- [10] W.Z. Cai, S. Shastri, IEEE Electron. Device Lett. 25 (2004) 468-470.

- [11] V. Lehmann, W. Hönlein, H. Reisinger, A. Spitzer, H. Wendt, J. Willer, Thin Solid Films 276 (1996) 138–142.

- J. White, Thin Solid Thins 270 (1990) 136–142.

- [12] F. Roozeboom, R. Elfrink, J. Verhoeven, J. van den Meerakker, F. Holthuysen, Microelectron. Eng. 53 (2000) 581–584.

- [13] J. Klootwijk, A. Kemmeren, R. Wolters, F. Roozeboom, J. Verhoeven, E. van den Heuvel, in: Defects in High-k Gate Dielectric Stacks, E. Gusev (Ed.), NATO Science Series II, Springer, 2005, pp. 17–28.

- [14] H. Föll, M. Christophersen, J. Carstensen, G. Hasse, Mater. Sci. Eng. R 39 (2002) 93–141.

- [15] M. Ritala, M. Leskelä, in: H.S. Nalwa (Ed.), Handbook of Thin Film Materials, vol. 1, Academic Press, San Diego, CA, 2002, pp. 103–159.

- [16] M. Leskelä, M. Ritala, Angew. Chem. Int. Ed. 42 (2003) 5548– 5554.

- [17] T. Aaltonen, M. Ritala, Y.-L. Tung, Y. Chi, K. Arstila, K. Meinander, M. Leskelä, J. Mater. Res. 19 (2004) 3353–3358.

- [18] For a more complete description of the etching setup, see: www.ette.com (ET&TE Etch and Technology GmbH, Germany).

- [19] T. Suntola, Thin Solid Films 216 (1992) 84-89.

- [20] M. Ritala, M. Leskelä, J.-P. Dekker, C. Mutsaers, P.J. Soininen, J. Skarp, Chem. Vapor Deposition 5 (1999) 7–9.

- [21] H. Seidl, M. Gutsche, U. Schroeder, A. Birner, T. Hecht, S. Jakschik, J. Luetzen, M. Kerber, S. Kudelka, T. Popp, A. Orth, H. Reisinger, A. Saenger, K. Schupke, B. Sell, in: Proceedings of the IEDM, 2002, San Francisco, pp. 839–849.

- [22] V. Lujala, J. Skarp, M. Tammenmaa, T. Suntola, Appl. Surf. Sci. 82/ 83 (1994) 34–40.

- [23] S.-C. Ha, E. Choi, S.-H. Kim, J.S. Roh, Thin Solid Films 476 (2005) 252–257.

- [24] R.K. Ulrich, W.D. Brown, S.S. Ang, F.D. Barlow, A. Elshabini, T.G. Lenihan, H.A. Naseem, D.M. Nelms, J. Parkenson, L.W. Schaper, G. Morcan, IEEE Circuits Device (September) (2000) 17– 25.