## Pictures to: Kristallfehler in hochintegrierten Schaltkreisen aus Silizium Part 2

## (Crystal Lattice Defects in Highly Integrated Silicon Devices)

- In what follows you see the second part of the "Abbildungen" (Pictures) as they occur in the report. The scans were made from my still existing copy and some of the pictures were somewhat processed by me to improve clarity.

- The figure captions are included so there is no need for further text.

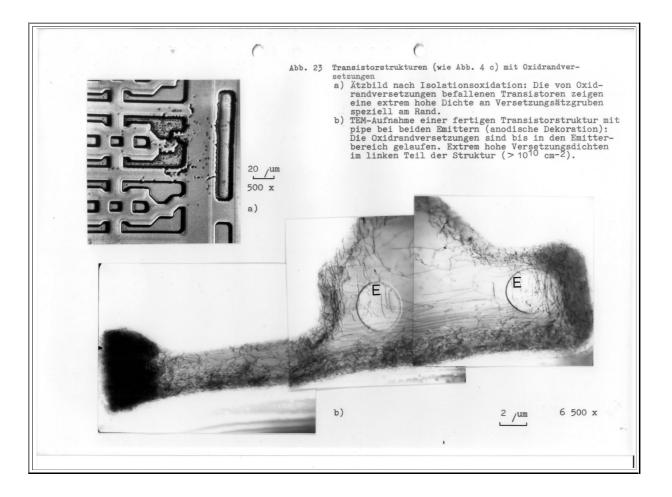

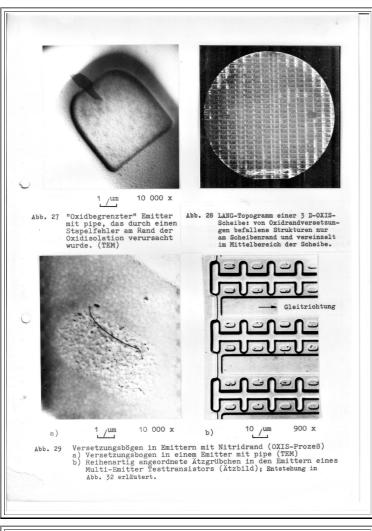

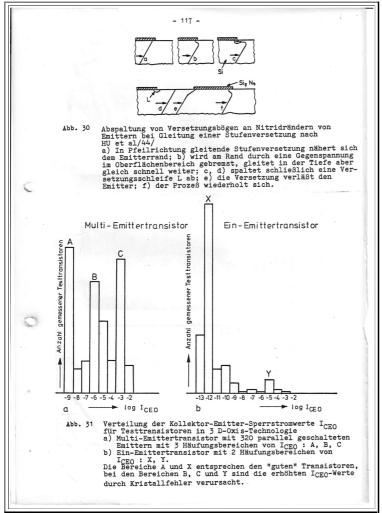

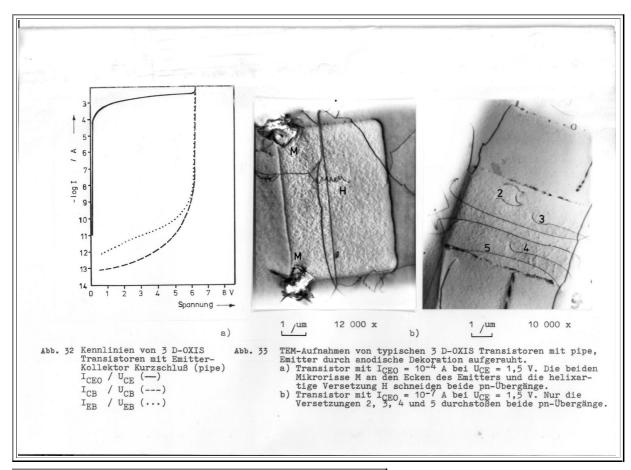

Here we have Fig. 23 Fig. 45

Abb. 25 TEM-Aufnahme eines Transistors mit oxidbegrenzten Emittern (E1, E2), von dem ein Emitter (E1) ein pipe aufweist.

Die anodische Dekoration hat bei E 1 bevorzugt an der Versetzung angegriffen (kleiner Trichter T erkennbar); die Versetzungen bei E 2 liegen unter dem Emitter- und Basisbereich.

[110] Gleitebenen der Versetzungen 4

4 500 x 5 /um

Relativ übersichtliche Anordnung von Oxidrandversetzungen im Transistorbereich (im TEM-Bild dunkel) und unter der Oxidisolation (heller Bereich). Die Versetzungen liegen parallel zur Oxid-Nitridkante, gleiten auf (111) oder (111) Ebenen ins Silizium, sind vom 60 ° Typ und haben Burgersvektoren, die 45 ° zur (001) Oberfläche geneigt sind (siehe Skizze). Abb. 26

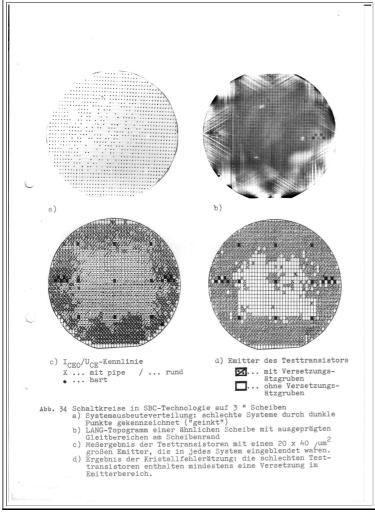

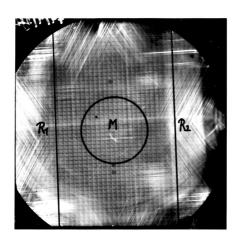

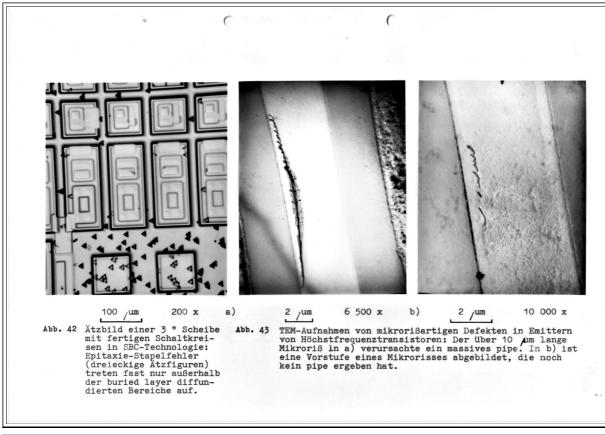

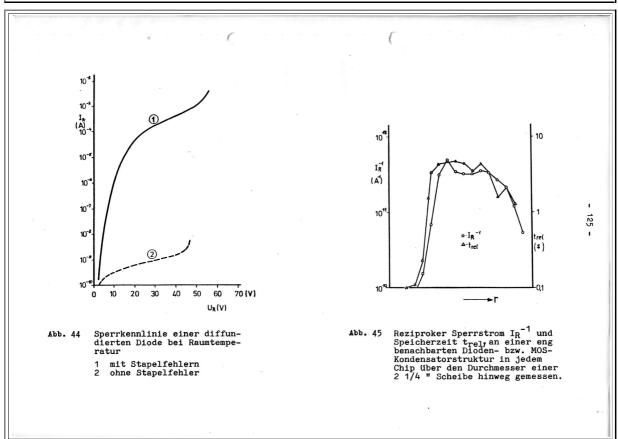

Abb. 41 LANG-Topogramm einer 2 " Scheibe mit ausgedehnten Gleitbereichen am Scheibenrand. In den Bereichen R1 und R2 mit hoher Versetzungsdichte fielen 55 % der gekapselten Schaltkreise wegen zu hoher Prasselspannung aus. Im gleitungsfreien Bereich M wurden nur 5 % Prasselausfälle festgestellt.

Continue with Fig. 45 - 71